Paper

딥러닝을 활용한 반도체 웨이퍼 불량 유형 구분 모델에 관한 연구(백선재, 이민혁)

Summary

0. Abstract

- 기존 산업현장에서는 반도체 웨이퍼 맵을 직접 확인하여 불량을 선별한다. 육안을 통한 웨이퍼 선별과정은 폭증하는 시장의 수요를 충족시킬 수 없다. 따라서 인간보다 신속, 정확한 반도체 웨이퍼 불량을 검출하여 자동화에 기여할 수 있는 AI 기술을 제시한다. 이를 위해 다층퍼셉트론(MLP)과 합성곱 신경망(CNN)을 기반으로 한 2가지 인공지능 모델을 고안하였고, 실험 결과 CNN 모델이 정확도가 평균 6.4% 더 높았음을 확인했다.

1. Introduction

- 반도체 칩은 수많은 제조공정을 거친 뒤 마지막 절차인 테스트를 통해 양품, 불량품을 선별한다. 반도체 수율 향상과 직결된

EDS(Electrical Die Sorting)공정은 전기적 특성 검사를 통해 개별 칩들이 원하는 품질 수준에 도달했는지를 확인하는 공정이다. - EDS Test는 전기적 특성 검사를 통해 각각의 칩들이 원하는 품질 수준에 도달하는지 체크한다. 그 후 양품 가능 여부를 판단해 수선(Repair) 가능한 칩은 다시 양품으로 만들고, 불가능한 칩은 특정 표시(Inking)를 통해 불량으로 판정한다. 불량으로 판정된 칩은 이후 공정에서 제외되어 효율을 높일 수 있다.

- 반도체 공정에서 EDS Test를 반드시 실행해야 하는 이유는 웨이퍼 제조 공정상의 문제점이나 설계상의 문제점을 조기에 발견하여 공정 및 설계 팀에 피드백을 줄 수 있기 때문이다.

2-1. Data

- 원본 데이터는 실제로 수집된 웨이퍼 맵의 유형에 생성적 대립신경망을 활용하여 유형 간 샘플 수의 균형을 유지한 'Mixed-type Wafer Defect Datasets'(Institute of Intelligent Manufacturing, Donghua University)을 입력 데이터로 한다.

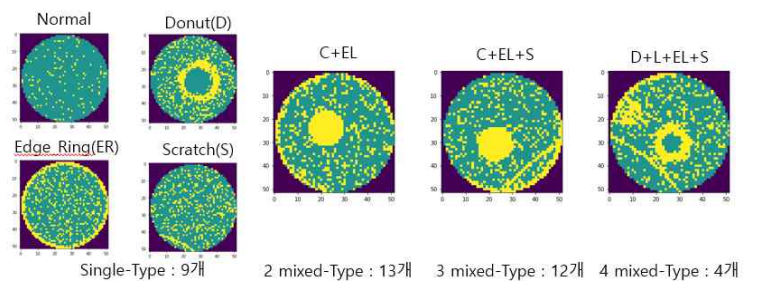

- Wafer Map Defect 52 X 52 픽셀이며 0(보라색)은 빈자리, 1(청록색)은 EDS 테스트 통과 칩, 2(노란색)은 불량 칩으로 해석할 수 있다.

- 싱글타입의 결함 패턴은 Center(C), Donut(D), Edge_Loc(EL), Edge_Ring(ER), Loc(L), Near_Full(NF), Scratch(S), Random(R)로 8가지 + 2가지가 혼합된 결함 패턴 13가지, 3가지가 혼합된 결합 패턴 12가지, 4가지가 혼합된 결함 패턴은 4가지로 구성

- 38개의 결함 패턴에 총 데이터 수는 3만8천개(각 결함 패턴당 1,000개씩 이미지 데이터 존재)

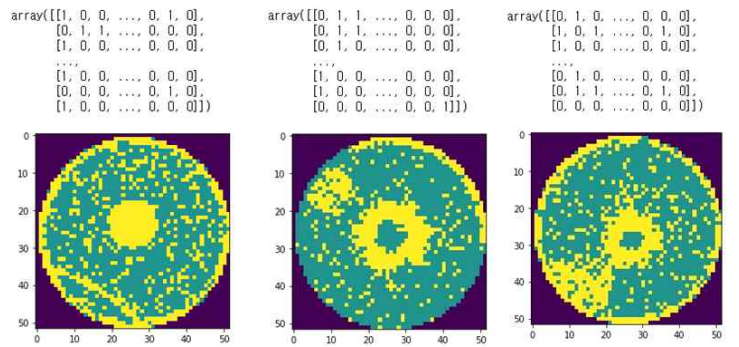

- 원본 데이터 세트의 경우 패턴 라벨 순서대로 인덱스가 묶여서 Shuffle을 통해 학습 정확도를 높였다.

- 훈련용 데이터 셋과 평가용 데이터 셋은 8:2의 비율로 나눴으며 평가의 정확도를 높이기 위해 스케일링을 진행하였다.

2-2. 다층 퍼셉트론(MLP)과 합성곱 신경망(CNN)

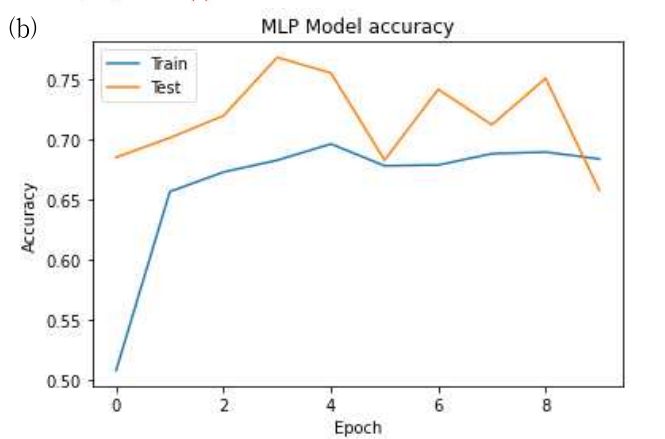

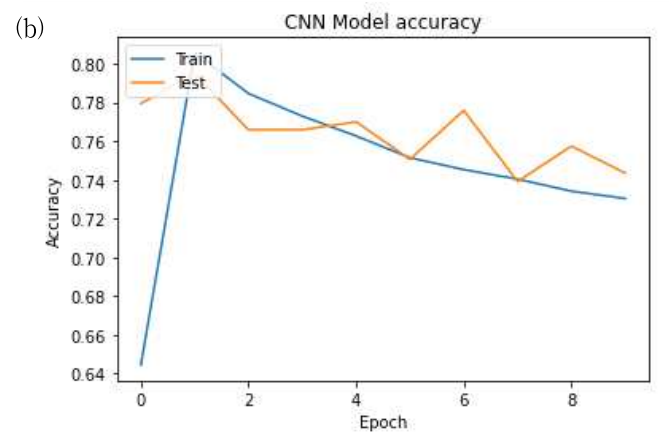

- 두 모델의 학습 횟수를 10회로 제한하여 학습시킨 결과

다층 퍼셉트론 모델(MLP)대비합성곱 신경망(CNN)의 정확도 성능은 평균 6.4% 이상 좋았다. 이는 평균적으로 74%에 해당하였다.

3. Conclusion

| model | 1 | 2 | 3 | 4 | 5 |

|---|---|---|---|---|---|

| 다층퍼셉트론 | 0.6146 | 0.7308 | 0.6913 | 0.5845 | 0.7012 |

| 합성곱 신경망 | 0.7468 | 0.7247 | 0.7275 | 0.7226 | 0.7217 |

- 합성곱 신경망(CNN)을 기반으로 한 모델이 정확도가 평균 6.4%가 높다.

- 보안상의 이유로 실제 국내 파운드리 기업에서의 원본 데이터를 활용하지 못한 한계점이 있다.